-

Notifications

You must be signed in to change notification settings - Fork 1

04_Qfsm a Icestudio

Vamos a intentar explicar como podemos crear una máquina de estados finitos desde el programa Qfsm , exportarlo a un fichero verilog y aprovechar este, para introducirlo, como un módulo Icestudio que será cargado en un ejemplo .ice y así, grabarlo en nuestra FPGA.

- Software Qfsm, podemos seguir las instrucciones para su descarga en Qfsm

- Software Icestudio Icestudio

- Nuestra FPGA favorita soportada por Icestudio Boards soportadas

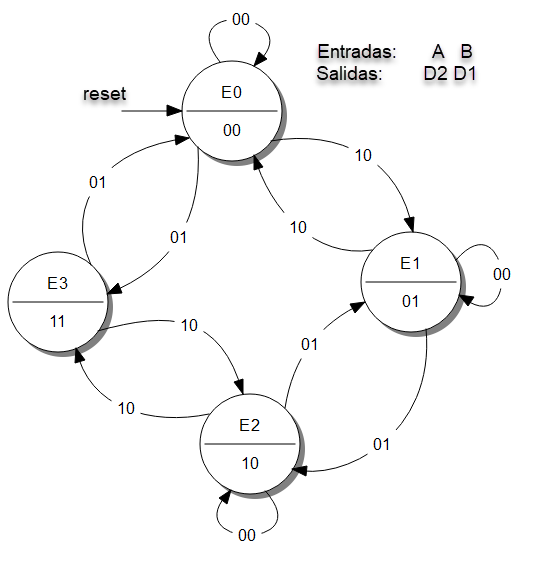

Vamos a realizar el siguiente Diagrama de estados como ejercicio didáctico.

Tendremos dos pulsadores A y B como valores de entrada y dos leds D2 D1 como salidas del sistema.

Desde Qfsm

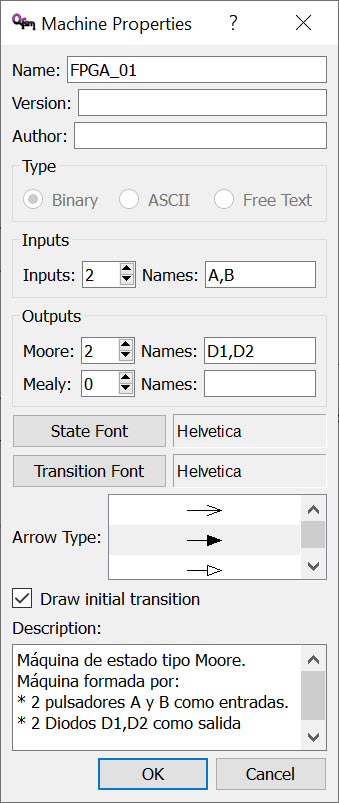

Creamos una nueva máquina de estados File-->New donde especificamos el nombre, cuantas entradas tenemos y salidas Moore/Mealy que contiene, también podemos añadir una pequeña descripción de nuestro sistema.

En nuestro caso configuramos:

- 2 entradas A B

- 2 salidas Moore (El valor de salida depende única y exclusivamente del esrtado en el que nos encontramos)

- Añadimos una pequeña descripción

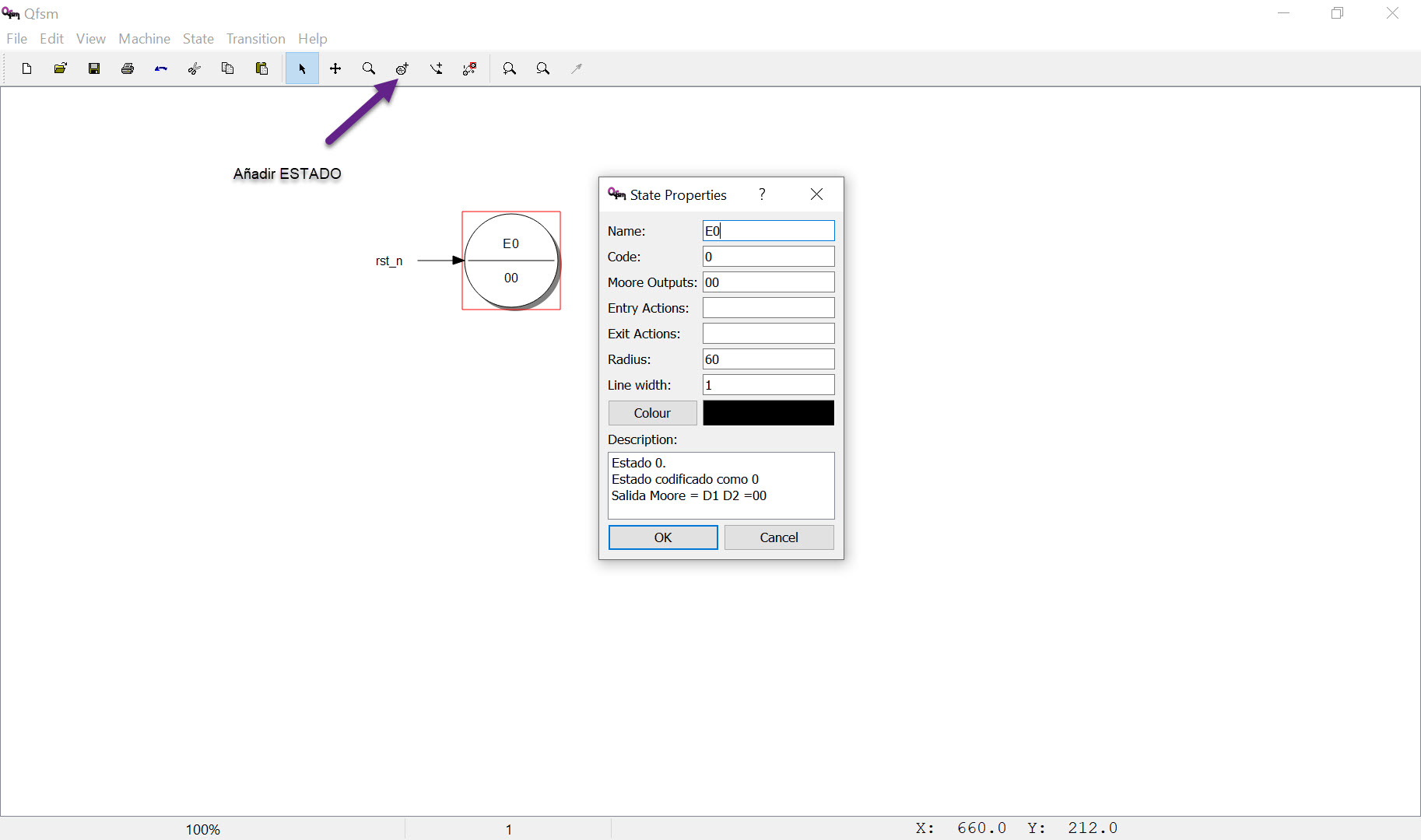

Empezaremos por introducir los Estados desde el menú State-->New o desde el botón rápido de Add State

Para cada estado, configuraremos en otras cosas, el nombre del estado, el código binario que se le asigna a dicho estado, valor que asignamos a las salidas Moore cuando nos encontramos en dicho estado, tamaño y grosor de la línea,etc.

Continuamos añadiendo las transiciones desde el menú Transition-->New o desde el botón rápido de Add Transition A continuación podemos ver un ejemplo de como se añaden transiciones:

Con la herramienta de selección podemos mover los estados y las flechas de las transiciones a nuestro gusto para que quede todo ordenado.

Una vez montado nuestro diagrama de estados, se puede simular desde el menú ** Machine-->Simulate** o desde el menú rápido de simulate

Podemos ver la simulación en el siguiente fichero GIF

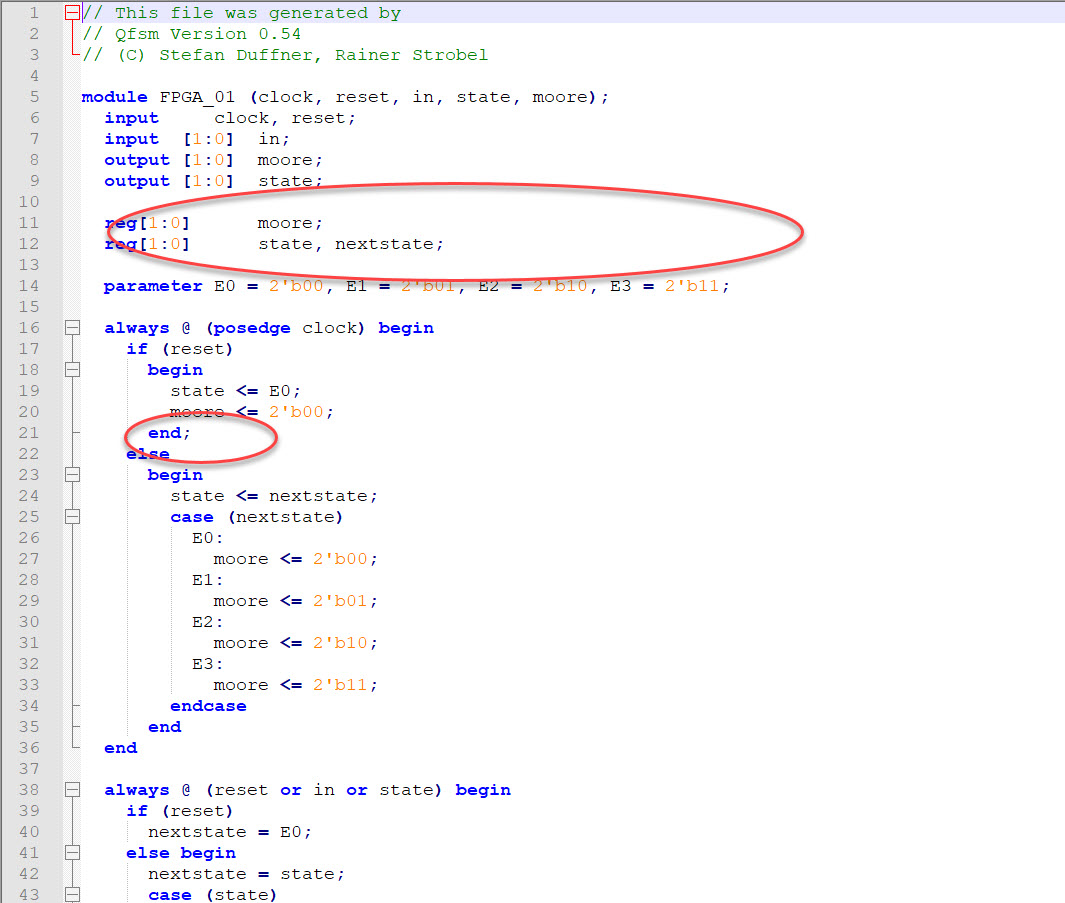

Qfsm nos permite exportar a Verilog desde el menú File-->Export-->verilog HDL... Tras la exportación, habremos creado un fichero FPGA_01.v (nombre elegido para este ejemplo)

Una vez exportado, hay que editar el fichero verilog y corregir dos detalles:

- Inicializar los registros a cero.

- Elmiminar punto y coma que añade de más en el primer "end" del primer bloque "always"

Llegados aquí, habremos terminado con Qfsm y empezaremos a trabajar con Icestudio.

Desde Icestudio, crearemos un bloque de código donde incluiremos el fichero verilog exportado con la directiva //@include fichero.v y creando una instancia de nuestra máquina de estados finitos llamando al módulo que contiene nuestra máquina. Añadiremos entradas y salidas necesarias a nuestro bloque de código teniendo así terminado nuestro módulo (contiene la máquina de estado finitos).

En la siguiente figura vemos como se crea el módulo:

Con el módulo que contiene nuestra máquina de estados, creamos un ejemplo donde añadimos las entradas para los pulsadores A y B( Sincronización-debouncer y detector de flanco ) así como las salidas a los diodos D2, D1.

Conectaremos los pulsadores a los puertos de entrada configurados ( Pmod1 (A) y Pmod7 (B) en mi IceStick ) y cargaremos el ejemplo.

En el siguiente GIF podemos ver el resultado obtenido.

Hemos podido ver como podemos integrar Qfsm a Icestudio y beneficiarnos de ambos para realizar máquinas de estado de forma sencilla.